導語:此專利碳化硅肖特基二極管的制造方法,在保證阻斷電壓的基礎上,增大肖特基二極管的陽極接觸區域面積,降低電子元件導通電阻。

受SiC(碳化硅)半導體應用領域擴大以及行業宏觀政策利好、資本市場追捧、地方積極推進等因素影響,國內第三代半導體產業推進較為迅速,2019年3月29日,由泰科天潤半導體科技(北京)有限公司投資建設的6寸半導體碳化硅電力電子器件生產線項目正式簽約落戶九江經開區。為九江市打造千億電子電器產業集群和壯大經開區首位產業注入新動能。積極發展在SiC晶圓上實現半導體功率器件的制造工藝。

據了解,泰科天潤半導體科技(北京)有限公司是國內第一家致力于第三代半導體材料碳化硅(SiC)電力電子器件制造的高新技術企業,總部坐落于中國北京中關村,在北京擁有一座完整的半導體工藝晶圓廠,可在4英寸SiC晶圓上實現半導體功率器件的制造工藝,并擁有目前國內唯一一條碳化硅器件生產線。

該項目總投資10億元,在城西港區建設6英寸半導體碳化硅電力電子器件生產線,規劃生產能力達到6萬片/年,項目滿產后,預計可實現年產值10.5億元。該項目屬于國家鼓勵發展的半導體行業,是我國近期重點發展的戰略性新興產業項目,項目將建成國內首條國際先進水平的SiC功率器件生產線,填補九江乃至江西省半導體功率器件的空白。

在電子器件領域,肖特基二極管廣泛應用于模擬電路、大規模集成電路,具有短反向恢復時間和極小的反向恢復電荷的特點,而電子器件的效率提升廣泛依賴于半導體材料發展。碳化硅作為新興的第三代半導體材料,具有良好的物理特性和電學特性,以其寬禁帶、高熱導率和高臨界電場等優點,成為制作高溫、大功率、高頻半導體器件的理想材料,因此推動了肖特基勢壘二極管和結勢壘二極管的發展。肖特基二極管利用反偏PN結的空間電荷區,為SBD結構承受反向偏壓,從而能夠在保證阻斷電壓的基礎上,適當降低肖特基勢壘高度以降低正向壓降,同時減小二極管反偏漏電。然而,由于在結勢壘肖特基二極管中,離子注入結區域并不能夠導電,因此器件的有效導通面積減小,這一缺點限制了JBS器件導通電流密度的提高。

為解決這一問題,泰科天潤公司于2018年2月12日提出了一項名為“一種碳化硅肖特基二極管及其制備方法”的發明專利(申請號:201810145243.2),申請人為泰科天潤半導體科技(北京)有限公司。

此專利提供了一種碳化硅肖特基二極管及其制備方法,利用溝槽結構,在保證阻斷電壓的基礎上,增大肖特基二極管的陽極接觸區域面積,降低器件導通電阻。

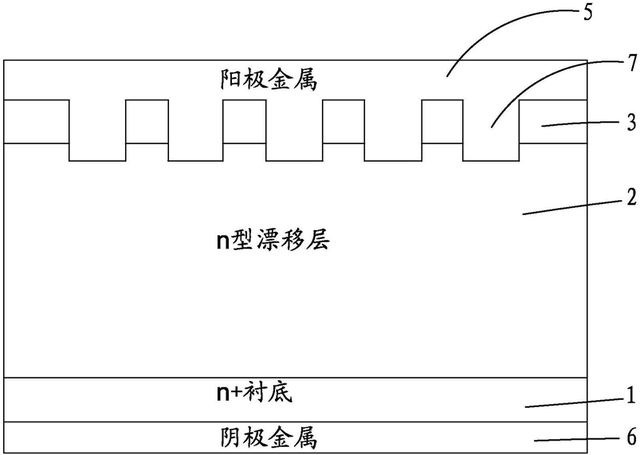

圖1 碳化硅肖特基二極管截面圖

此專利提出的碳化硅肖特基二極管截面如圖1所示,包括從上到下依次設置的陽極金屬5、p型外延層3、n型漂移層2、n+襯底1以及陰極金屬6。在p型外延層3上設有復數個溝槽,陽極金屬5一側面設有復數個突起部7,溝槽與突起部相匹配。n型外延層的厚度為5um至200um,p型外延層3的厚度為0.3um至1.5um,其中n型外延層的摻雜濃度大于p型外延層摻雜濃度。陰極金屬為Ni,陽極金屬為Al或Ti,以更好地形成陽極接觸,金屬與n型漂移層2形成肖特基接觸,與p型外延層3形成歐姆接觸,這樣當器件反向阻斷時,由n型漂移層2和p型外延層3形成的耗盡層能夠最大程度地屏蔽溝槽4側面,降低阻斷狀態下的漏電流。

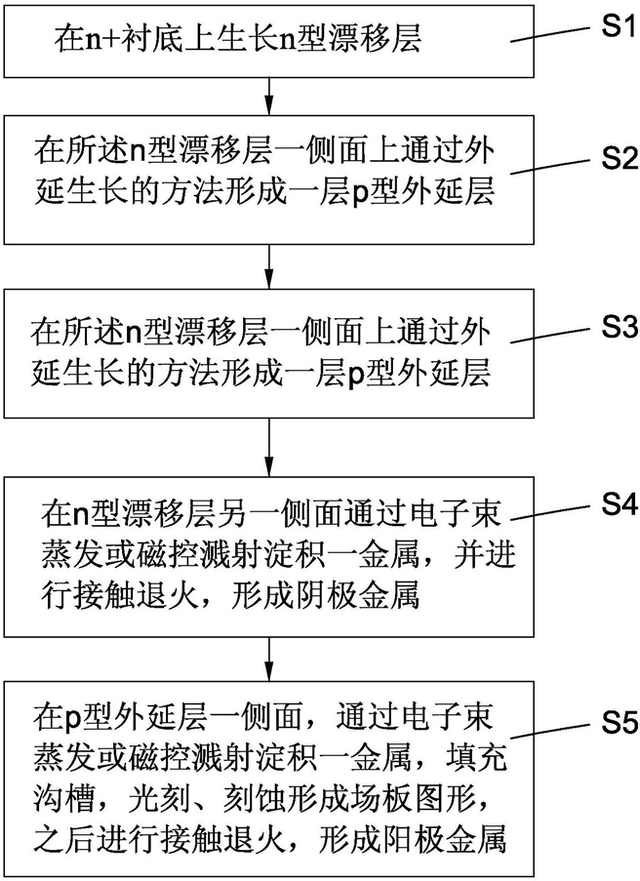

圖2 碳化硅肖特基二極管的制備方法的流程圖

碳化硅肖特基二極管的制備方法如圖2所示,首先在在n+襯底1上生長n型漂移層,并在n型漂移層一側面上通過外延生長的方法形成一層p型外延層,然后在p型外延層一側面的表面通過電子束蒸發的方法,蒸發形成設定厚度的掩膜層,利用掩膜層和氧化層形成溝槽。之后在n型漂移層2另一側面通過電子束蒸發或磁控濺射淀積一金屬,通過退火處理形成陰極金屬;在p型外延層3一側面,通過電子束蒸發或磁控濺射淀積一金屬,填充溝槽,光刻、刻蝕形成場板圖形,之后在氮氣保護下進行接觸退火,形成陽極金屬5,最后形成完整的碳化硅肖特基二極管。

美瑞電子(0769-21665206)為泰科天潤代理商,歡迎咨詢碳化硅肖特基二極管、碳化硅MOSFET和碳化硅模塊相關電子元件。